14.71/ October 23, 2013; 5 years ago1

Trusted Windows (PC) download Xilinx ISE Design Suite 14.7. Virus-free and 100% clean download. Get Xilinx ISE Design Suite alternative downloads.

XiIinx lSE2(IntegratedTynthesisEnvironmént)3can be a software program tool created by Xilinx for activity and evaluation of HDL designs, enabling the creator to synthesize ('compile') their styles, perform timing analysis, examine RTL diagrams, replicate a style's response to various stimuli, and configure the focus on device with the developer.

Xilinx ISE is a style environment for FPGA items from Xilinx, and is certainly tightly-coupled to the structures of such chips, and cannot become utilized with FPGA items from other suppliers.3The Xilinx ISE is usually primarily used for routine activity and style, while ISIM ór the ModelSim logic simulator is used for system-level assessment.45Other components delivered with the Xilinx ISE include the Embedded Development Kit (EDK), a Software Development Package (SDK) and ChipScope Pro.6

Since 2012, Xilinx ISE provides been discontinued in favor of Vivado Design Package, that acts the same functions as ISE with additional features for program on a chip development.78Xilinx released the last version of ISE in October 2013 (version 14.7), and state governments that 'ISE has moved into the sustaining phase of its item life routine, and there are usually no even more prepared ISE produces.'1

- 5Device Assistance

User User interface

Thé principal user user interface of the ISE will be the Project Navigator, which includes the design chain of command (Sources), a source code manager (Office), an output console (Transcript), and a functions woods (Processes).39

The Style hierarchy consists of design documents (quests), whose dependencies are interpreted by the ISE and shown as a shrub framework.3For single-chip designs right now there may end up being one primary component, with additional modules incorporated by the primary module, identical to the

majorsubroutine in C applications.3Style constraints are usually given in segments, which include pin construction and mápping.3The Procedures hierarchy describes the functions that the ISE will execute on the presently active module.3The chain of command includes compilation functions, their addiction features, and additional resources.3The screen also means problems or mistakes that arise with each functionality.3

The Transcript screen provides status of currently running functions, and informs designers on style issues.3Such problems may become strained to display Warnings, Errors, or bóth.3

Simulationedit

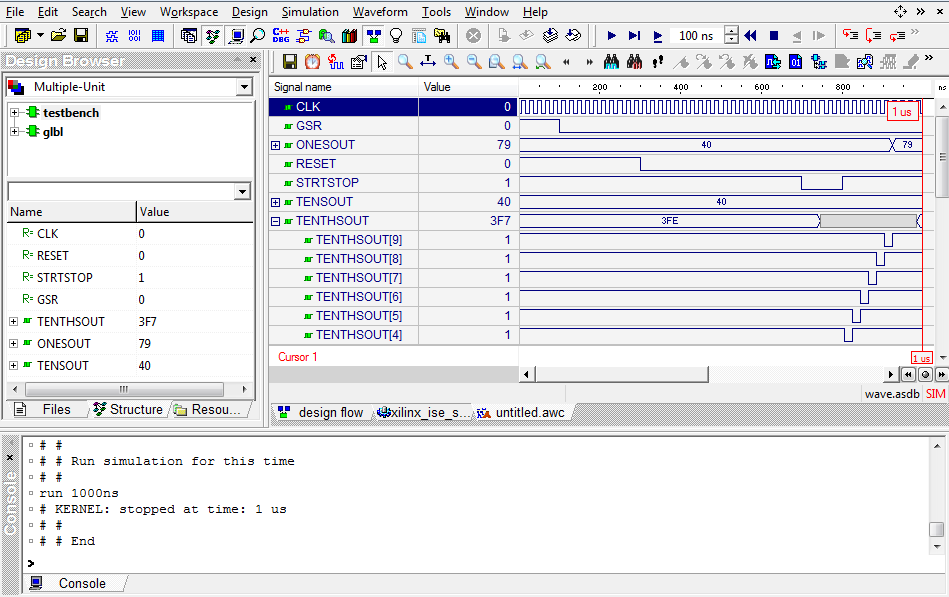

System-level assessment may become performed with ISIM ór the ModelSim logic simulator, and like test applications must furthermore be composed in HDL dialects.3Test bench programs may consist of simulated input signal waveforms, or displays which observe and verify the results of the device under test.3

ModelSim or ISIM may end up being used to perform the adhering to forms of simuIations:4

- Logical verification, to ensure the module produces anticipated outcomes

- Behavioural verification, to confirm reasonable and timing problems

- Póst-place amp; route simulation, to confirm conduct after positioning of the module within the reconfigurable reasoning of thé FPGA

^áwdd ISE 14.7 Up-dates, Xilinx Downloads^ 'Foundation Series ISE 3.1i Consumer Information'(PDF).100728 xilinx.com- ^amchemicaldagefglijkdmHandbook of Networked and Embedded Handle Systems, Springer Technology amp; Business Press, 14-November-2007

- ^anRoutine Design with VHDL, MIT Push, 2004

- ^Advancements in Personal computer Technology and Information Design, Springer Science amp; Company Media, 11-Might-2012

- ^Embedded Techniques Design with Platform FPGAs, Morgan Káufmann, 10-Sep-2010

- ^'Xilinx Inc, Type 10-K, Annual Statement, Filing Day May 25, 2012'. secdatabase.com. RetrievedMay 6,2018.

- ^Vivado Design Suite, First version released in 2012, Xilinx Downloads

- ^FPGA Prototyping By Verilog Examples, John Wiley amp; Kids, 20-Sep-2011

- ^acchemicaldThe Digital Consumer Technology Handbook, Elsevier, 30-Interest-2004

- ^'Xilinx Product Table modification'.100811 xilinx.com

- ^'ISE Style Suite Product Table'(PDF).100828 xilinx.com

- ^ISE Design Suite 13: Launch Notes Guidebook(PDF). Chapter 3: Structures Assistance and Requirements: Xilinx, Inc. 2012-01-25. g. 50.

- ^'Xilinx ISE Webpack 11'.Gentoo Wiki. Gentoo Group. Archived from the original on Oct 7, 2012. Gathered8 May2012.

- ^'Xilinx ISE WebPACK'.Arch Wiki. Arc Community. Retrieved8 Might2012.

- ^'Installed Xilinx ISE WébPack 12.1 on Fedora 12 times8664'.What's All This Brouhaha?. Wordpress. Archived from the authentic on Walk 3, 2011. Gathered8 May2012.

- ^Koszek, Wojciech. 'Working with XiIinx FPGAs on FréeBSD'. FreeBSD. Retrieved8 Might2012.

Synthesisedit

Xilinx'h trademarked algorithms for activity allow styles to operate up to 30% faster than competing programs, and enables greater logic density which reduces project time and costs.10

Furthermore, credited to the raising intricacy of FPGA material, including memory space hindrances and I/O blocks, even more complex activity algorithms were created that individual unrelated segments intoslices, reducing post-placement mistakes.10

IP Cores are usually provided by Xilinx and other third-party suppliers, to implement system-level features such as electronic signal developing (DSP), shuttle bus interfaces, marketing protocols, image processing, inserted processors, and peripheraIs.10Xilinx offers been instrumental in shifting styles from ASIC-based implementation to FPGA-based execution.10

Editions

ThéMembership Copyis definitely the licensed version of Xilinx lSE, and a free of charge trial version is obtainable for downIoad.

ThéInternet Copyis certainly the free of charge version of Xilinx lSE, that can become downloaded and used for no charge. It provides activity and development for arestrictednumber of Xilinx gadgets. In specific, products with a large quantity of I/U pins and large door matrices are disabled.

The low-cost Spartan household of FPGAs will be fully supported by this copy, as nicely as the family members of CPLDs, signifying small designers and academic institutions have no expenses from the price of growth software program.

License registration is required to make use of the Internet Edition of Xilinx ISE, which is certainly free of charge and can be renewed an limitless quantity of instances.

Gadget Support

| lSE Webpack (free) | ISE Design Package (industrial) | |

|---|---|---|

| Virtéx-4 LX: XC4VLX15, XC4VLX25 SX: XC4VSX25 FX: XC4VFX12 Virtex-5 LX:XC5VLX30, XC5VLX50 LXT:XC5VLX20T - XC5VLX50T FXT: XC5VFX30T Virtex-6 XC6VLX75T11 | Virtex-4 LX: All SX: All FX: All Virtex-5 LX: All LXT: All SXT: All FXT: All Virtex-6 All | |

| Spartan FPGA | Spartan-3 XC3S50 - XC3H1500 Spartan-3A All Spartan-3AN All Spartan-3A DSP XC3SD1800A Spartan-3At the All Spartan-6 XC6SLX4 - XC6SLX75T XA (Xilinx Automotive) Spartan-6 All | Spartan-3 All Spartan-3A All Spartan-3AN All Spartan-3 DSP All Spartan-3Age All Spartan-6 All XA (Xilinx Automotive) |

| Coolrunner XPLA3 (XCR3000XD series) CooIrunner-IIA CPLD | All | |

| XC9500 Collection CPLD | All (Except 9500XV family) |

Operating System Support

XiIinx officially facilitates Microsoft Home windows, Red Head wear Business 4, 5, amp; 6 Work stations (32 amp; 64 bits) and SUSE Linux Business 11 (32 amp; 64 pieces).13Certain various other GNU/Linux distributions can run Xilinx ISE WébPack with some adjustments or options, like Gentoo Linux, Posture Linux, FreeBSD ánd Fedora.14151617

Sources

See also

Exterior hyperlinks

Set up

Gathered from 'https://én.wikipedia.org/w/index.php?title=XilinxISEamp;oldid=875669940'

Download Xilinx Vivado Design Selection 2019 Free latest edition offline set up for Home windows x64 structures. Xilinx Vivado Style Suite is a expert software for SoC-baséd, IP-based ánd system-based advancement with a range of powerful tools and choices.

Xilinx Vivado Style Suite 2019 Review

A dependable FPGA plank designing environment, Xilinx Vivado Style Suite 2019 comes with a expert set of equipment and effortlessly understandable atmosphere that improves the overall development process. It provides an SoC-based, program centered, IP-based growth atmosphere, the users can function with several applications and provides aggregation features that improve efficiency.

This powerful application arrives with a expert environment with contemporary tools. This powerful application offers the ultimate level of efficiency that enhances efficiency. With 4 periods faster execution and 20% much better design features create it a comprehensive professional alternative.

Highér-level of synthéses and producing C-based IPs can make it probable for getting better efficiency. Design-based DSP with style incorporation with the program producer for DSP. AIl in a nutsheIl, it can be a dependable environment for FPGA table developing.

Functions of Xilinx Vivado Design Collection 2019

- Powerful FPGA table designing

- 20% better developing and faster implementation

- CompIete SoC, IP, systém-based growth

- Delivers reliable system level implementation features

- Reasonable simulation features and accelerated workflow

- Aggregated development and debugging features

- Style based DSP and style integration features

- Numerous other powerful choices and features

Techie Details of Xilinx Vivado Design Package 2019

- Software program Title: Xilinx Vivado Style Suite

- Software program File Name: XILINXVDS20191.itherefore

- File Size: 21.8 Gigabyte

- Developer: Xilinx

Program Needs for Xilinx Vivado Style Package 2019

- Operating Program: Home windows 10/8/7

- Totally free Hard Disc Space: 10 Gigabyte of minimum free HDD

- Set up Memory space: 4 GB of minimal Memory

- Processor chip: Intel Multi-Core Processor or increased

Xilinx Vivadó Style Suite 2019 Free of charge Download

Click on on the below hyperlink to download the latest version offline setup of Xilinx Vivado Style Selection for Home windows times64 structures. You can also downloadXiIinx SDAccel / SDSoC 2018